often describe this ramp via the easy-to-remember relationship

$$C\Delta v = I\Delta t$$

SECTION 10.1 Sine Wave Generators

or "cee delta vee equals aye delta tee." This allows us to estimate the time it takes to effect a constant-rate change  $\Delta v$  as

$$\Delta t = \frac{C}{I} \Delta v \tag{10.2}$$

An exponential transient occurs when C is charged or discharged via a series resistance R. With reference to Fig. 10.1b, the instantaneous capacitance voltage is

$$v(t) = V_{\infty} + (V_0 - V_{\infty}) \exp[(t - t_0)/\tau]$$

where  $V_0$  is the initial voltage,  $V_\infty$  is the steady-state voltage that would be reached in the limit  $t \to \infty$ , and  $\tau = RC$  is the time constant governing the transient. This equation holds regardless of the values and polarities of  $V_0$  and  $V_\infty$ . The transient reaches a specified intermediate value  $V_1$  at an instant  $t_1$  such that  $V_1 = V_\infty + (V_0 - V_\infty) \exp[(t_1 - t_0)/\tau]$ . Taking the natural logarithm of both sides and solving for  $\Delta t = t_1 - t_0$  allows us to estimate the time it takes to charge or discharge C from  $V_0$  to  $V_1$  as

$$\Delta t = \tau \ln \frac{V_{\infty} - V_0}{V_{\infty} - V_1} \tag{10.3}$$

As we proceed, we shall make frequent use of these equations.

## 10.1 SINE WAVE GENERATORS

The sine wave is certainly one of the most fundamental waveforms—both in a mathematical sense, since any other waveform can be expressed as a Fourier combination of basic sine waves, and in a practical sense, since it finds extensive use as a test, reference, and carrier signal. In spite of its simplicity, its generation can be a challenging task if near-purity is sought. The op amp circuits that have gained the most prominence in sine wave generation are the *Wien-bridge oscillator* and the *quadrature oscillator*, to be discussed next. Another technique, based on the conversion of the triangular to the sine wave, will be discussed in Section 10.4.

# **Basic Wien-Bridge Oscillator**

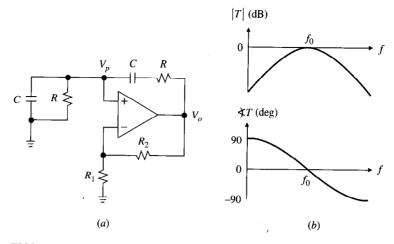

The circuit of Fig. 10.2a uses both negative feedback, via  $R_2$  and  $R_1$ , and positive feedback, via the series and parallel RC networks. Circuit behavior is strongly affected by whether positive or negative feedback prevails. The components of the RC networks need not be equal-valued; however, making them so simplifies analysis as well as inventory.

**FIGURE 10.2** Wien-bridge circuit and its loop gain T(jf) for the case  $R_2/R_1 = 2$ .

The circuit can be viewed as a noninverting amplifier that amplifies  $V_p$  by the amount

$$A = \frac{V_o}{V_p} = 1 + \frac{R_2}{R_1} \tag{10.4}$$

where we are assuming an ideal op amp for simplicity. In turn,  $V_p$  is supplied by the op amp itself via the two RC networks as  $V_p = [Z_p/(Z_p + Z_s)]V_o$ , where  $Z_p = R \parallel (1/j2\pi fC)$  and  $Z_s = R + 1/j2\pi fC$ . Expanding, we get

$$B(jf) = \frac{V_p}{V_o} = \frac{1}{3 + j(f/f_0 - f_0/f)}$$

(10.5)

where  $f_0 = 1/2\pi RC$ . The overall gain experienced by a signal in going around the loop is T(jf) = AB, or

$$T(jf) = \frac{1 + R_2/R_1}{3 + j(f/f_0 - f_0/f)}$$

(10.6)

This is a band-pass function since it approaches zero at both high and low frequencies. Its peak value occurs at  $f=f_0$  and is

$$T(jf_0) = \frac{1 + R_2/R_1}{3} \tag{10.7}$$

The fact that  $T(jf_0)$  is real indicates that a signal of frequency  $f_0$  will experience a net phase shift of zero in going around the loop. Depending on the magnitude of  $T(jf_0)$ , we have three distinct possibilities:

1.  $T(jf_0) < 1$ , that is, A < 3 V/V. Any disturbance of frequency  $f_0$  arising at the input of the op amp is first amplified by A < 3 V/V, and then by  $B(jf_0) = \frac{1}{3}$  V/V, for a net gain of less than unity. Intuition tells us that this disturbance lessens each time it goes around the loop until it eventually decays to zero. We can state that negative feedback (via  $R_2$  and  $R_1$ ) prevails over positive feedback (via  $R_2$ )

and  $Z_p$ ), resulting in a stable system. Consequently, the circuit poles lie in the left half of the complex plane.

SECTION 10.1 Sine Wave Generators

left half of the complex plane.

T(jf<sub>0</sub>) > 1, that is, A > 3 V/V. Now positive feedback prevails over negative feedback, indicating that a disturbance of frequency f<sub>0</sub> will be amplified regeneratively, causing the circuit to break out into oscillations of growing magnitude. The circuit is now *unstable*, and its poles lie in the right half of the complex plane. As we know, the oscillations build up until the saturation limits of the op amp are reached. Thereafter, v<sub>O</sub> will appear as a clipped sine wave when observed with the oscilloscope or visualized via PSpice.

As we know, the oscillations build up until the saturation limits of the op amp are reached. Thereafter, v<sub>O</sub> will appear as a clipped sine wave when observed with the oscilloscope or visualized via PSpice.

3. T(jf<sub>0</sub>) = 1, or A = 3 V/V exactly, a condition referred to as neutral stability because positive and negative feedback are now applied in equal amounts. Any disturbance of frequency f<sub>0</sub> is first amplified by 3 V/V and then by ½ V/V, indicating that once started, it will be sustained indefinitely. As we know, this corresponds to a pole pair right on the jω axis. The conditions ≺T(jf<sub>0</sub>) = 0° and |T(jf<sub>0</sub>)| = 1 are together referred to as the Barkhausen criterion for oscillation at f = f<sub>0</sub>. The band-pass nature of T(jf) allows for oscillation to occur only at f = f<sub>0</sub>; any attempt to oscillate at other frequencies is naturally discouraged because ≺T ≠ 0° and |T| < 1 there. By Eq. (10.7), neutral stability is achieved with</li>

$$\frac{R_2}{R_1} = 2 \tag{10.8}$$

It is apparent that when this condition is met, the components around the op amp form a balanced bridge at  $f=f_0$ .

In a real-life circuit, component drift makes it difficult to keep the bridge exactly balanced. Moreover, provisions must be made so that (a) oscillation starts spontaneously at power turn-on, and (b) its amplitude is kept below the op amp saturation limits to avoid excessive distortion. These objectives are met by making the ratio  $R_2/R_1$  amplitude-dependent such that at low signal levels it is slightly greater than 2 to ensure oscillation start-up, and that at high signal levels it is slightly less than 2 to limit amplitude. Then, once the oscillation has started, it will grow and automatically

stabilize at some intermediate level where  $R_2/R_1 = 2$  exactly. Amplitude stabilization takes on many forms, all of which use nonlinear elements to either decrease  $R_2$  or increase  $R_1$  with signal amplitude. To provide an intuitive basis for our discussion, we shall continue using the function T(jf), but in an incremental sense because of the nonlinearity now present in the circuit.

# **Automatic Amplitude Control**

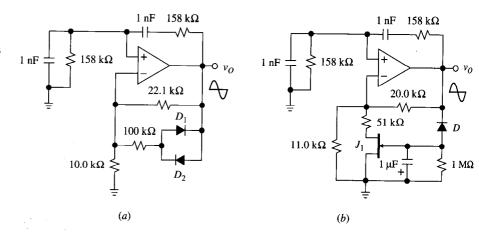

The circuit of Fig. 10.3a uses a simple diode-resistor network to control the effective value of  $R_2$ . At low signal levels the diodes are off, so the  $100\text{-k}\Omega$  resistance has no effect. We thus have  $R_2/R_1 = 22.1/10.0 = 2.21$ , or  $T(jf_0) = (1+2.21)/3 = 1.07 > 1$ , indicating oscillation buildup. As the oscillation grows, the diodes are gradually brought into conduction on alternate half-cycles. In the limit of heavy diode conduction,  $R_2$  would effectively change to  $(22.1 \parallel 100) = 18.1 \text{ k}\Omega$ , giving  $T(jf_0) = 0.937 < 1$ . However, before this limiting condition is reached, amplitude

CHAPTER 10 Signal Generators

FIGURE 10.3 Practical Wien-bridge oscillators.

will automatically stabilize at some intermediate level of diode conduction where  $R_2/R_1 = 2$  exactly, or  $T(jf_0) = 1$ . The process can be visualized via PSpice using the following file.

```

Wien-Bridge Oscillator:

Cp 3 0 1nF IC=0V

Rp 3 0 158k

Cs 3 36 1nF IC=0V

Rs 36 6 158k

R1 2 0 10k

R2 2 6 22.1k

R3 2 26 100k

D1 26 6 D1N4148

D2 6 26 D1N4148

.model D1N4148 D(Is=0.1p Rs=16 CJO=2p Tt=12n Bv=100 Ibv=0.1p)

.lib eval.lib

XOA 3 2 7 4 6 ua741

VCC 7 0 dc 15V

VEE 4 0 dc -15V

.tran 50us 15ms 0ms 50us UIC

.probe

.end

```

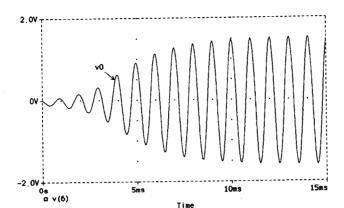

As shown in Fig. 10.4, the output stabilizes automatically at a peak amplitude  $V_{om} \cong 1.5 \text{ V}$ .

A disadvantage of the above circuit is that  $V_{om}$  is quite sensitive to variations in the diode-forward voltage drops. The circuit of Fig. 10.3b overcomes this drawback by using an n-JFET as the stabilizing element. At power turn-on, when the 1- $\mu$ F capacitance is still discharged, the gate voltage is near 0 V, indicating a low channel resistance. The JFET effectively shorts the 51-k $\Omega$  resistance to ground to give  $R_2/R_1\cong 20.0/(11.0\parallel 51)\cong 2.21>2$ , so oscillation starts to build up. The diode and the 1- $\mu$ F capacitance form a negative peak detector whose voltage becomes

progressively more negative as the oscillation grows. This gradually reduces the

FIGURE 10.4 Using PSpice to display the output of the circuit of Fig. 10.3a.

conductivity of the JFET until, in the limit of complete cutoff we would have  $R_2/R_1 = 20.0/11.0 = 1.82 < 2$ . However, amplitude stabilizes automatically at some intermediate level where  $R_2/R_1 = 2$  exactly. Denoting the corresponding gate-source voltage as  $V_{GS(crit)}$ , and the output peak amplitude as  $V_{om}$ , we have  $-V_{om} = V_{GS(crit)} - V_{D(on)}$ . For instance, with  $V_{GS(crit)} = -4.3$  V we get  $V_{om} \cong 4.3 + 0.7 = 5$  V.

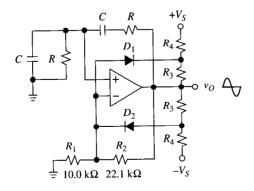

Figure 10.5 shows yet another popular amplitude-stabilization scheme,<sup>2</sup> this time using a diode limiter for easier programming of amplitude. As usual, for low output levels the diodes are biased in cutoff, yielding  $R_2/R_1 = 2.21 > 2$ . The oscillation grows until the diodes become conductive on alternate output peaks. Thanks to the symmetry of the clamping network, these peaks are likewise symmetric, or  $\pm V_{om}$ . To estimate  $V_{om}$ , consider the instant when  $D_2$  starts to conduct. Assuming the current through  $D_2$  is still negligible, and denoting the voltage at the anode of  $D_2$  as  $V_2$ , we use KCL to write  $(V_{om} - V_2)/R_3 \cong [V_2 - (-V_S)]/R_4$ , where  $V_2 = V_n + V_{D2(on)} \cong V_{om}/3 + V_{D2(on)}$ . Eliminating  $V_2$  and solving gives

FIGURE 10.5

Wien-bridge oscillator using a limiter for amplitude stabilization.

SECTION 10.1

Sine Wave

Generators

Signal Generators

$V_{om} \cong 3[(1+R_4/R_3)V_{D2(\text{on})}+V_S]/(2R_4/R_3-1)$ . For example, with  $R_3=3$  k $\Omega$ ,  $R_4=20$  k $\Omega$ ,  $V_S=15$  V, and  $V_{D(\text{on})}=0.7$  V, we get  $V_{om}\cong 5$  V.

#### **Practical Considerations**

The accuracy and stability of the oscillation are affected by the quality of the passive components as well as op amp dynamics. Good choices for the elements in the positive-feedback network are polycarbonate capacitors and thin-film resistors. To compensate for component tolerances, practical Wien-bridge circuits are often equipped with suitable trimmers for the exact adjustment of  $f_0$  as well as THD minimization. With proper trimming, THD levels as low as 0.01% can be achieved. We observe that because of the filtering action provided by the positive-feedback network, the sine wave  $v_P$  available at the noninverting input is generally purer than  $v_O$ . Consequently, it may be desirable to use  $v_P$  as the output, though a buffer would be needed to avoid perturbing circuit behavior.

To avoid slew-rate limiting effects for a given output peak-amplitude  $V_{om}$ , the op amp should have  $SR > 2\pi V_{om} f_0$ . Once this condition is met, the limiting factor becomes the finite GBP, whose effect is a downshift in the actual frequency of oscillation. It can be proved<sup>2</sup> that to contain this shift within 10% when a constant-GBP op amp is used, the latter should have  $GBP \ge 43 f_0$ . To compensate for this downshift, one can suitably predistort the element values of the positive-feedback network, in a manner similar to the filter predistortion techniques of Section 6.6.

The low end of the frequency range depends on how large the components in the reactive network can be made. Using FET-input op amps to minimize input-bias-current errors, the value of R can easily be increased to the range of tens of megohms. For instance, using  $C=1~\mu\mathrm{F}$  and  $R=15.9~\mathrm{M}\Omega$  gives  $f_0=0.01~\mathrm{Hz}$ .

## **Quadrature Oscillators**

We can generalize the above ideas and make an oscillator out of any second-order filter that is capable of giving  $Q=\infty$  as well as Q<0. To this end, we first ground the input, since it is no longer necessary; then, we design for an initially negative Q to force the poles in the right half of the complex plane and thus ensure oscillation startup; finally, we include a suitable amplitude-dependent network to automatically pull the poles back to the  $j\omega$  axis and give  $Q=\infty$ , or sustained oscillation.

Of special interest are filter topologies of the dual-integrator-loop type, since they provide two oscillations in quadrature, that is, with a relative phase shift of 90°. Figure 10.6 shows how a biquad filter can be turned into a quadrature oscillator. To save an op amp,  $OA_2$  is a noninverting, or Deboo, integrator with  $f_0 = 1/2\pi RC$ , and it is adjusted to make it slightly regenerative to ensure oscillation startup. At low signal levels  $OA_1$  is a lossless integrator with  $f_0 = 1/2\pi RC$ . However, as soon as signal amplitude has grown enough to activate the diode limiter,  $OA_1$  becomes lossy. Thereafter, the loss due to  $OA_1$  will compensate for the regeneration due to  $OA_2$ ,